Úvod

Prudký rozvoj elektroniky, ktorého sme v posledných rokoch svedkami prináša stále komplikovanejšie a rýchlejšie obvody. Aby sme boli schopní s takýmito obvodmi pracovať, potrebujeme stále výkonnejšie vybavenie. Cieľom tohoto článku je poskytnúť stručný úvod do problematiky priamych číslicových syntezátorov nasledovaný konštrukciou univerzálnych modulov, z ktorých sa dá postaviť signálový generátor na báze DDS. Tento nájde uplatnenie nielen medzi rádioamatérmi, ale napríklad aj v digitálnej komunite ako univerzálny zdroj hodinových signálov.

DDS moduly je možné využiť napríklad ako:

- lokálne oscilátory pre rádiostanice

- univerzálna preddelička so zlomkovým deliacim pomerom

- generátor „exotických“ hodinových frekvencií pre číslicové obvody

- generátor digitálnych signálov s riaditeľnou striedou

- generátor s veľmi jemným krokom ladenia napríklad pre meranie parametrov náhradnej schémy kryštálových rezonátorov

- nastavovanie frekvenčných filtrov

- ladenie medzifrekvenčných obvodov

- malý merací vysielač

Hardvér modulov bol rozdelený do logických celkov s ohľadom na dosiahnutie maximálnej univerzálnosti. Toto umožňuje pripojiť DDS modul napríklad ku jednoduchému mikrokontroléru pre amatérske použitie, alebo k rýchlemu FPGA obvodu pre časovo náročné špecifické aplikácie.

Celý generátor bol navrhovaný tak, aby sa dosiahol rozumný kompromis medzi dosiahnutými technickými parametrami a náročnosťou konštrukcie. V konštrukcii som sa snažil použiť len bežne dostupné súčiastky, ktoré boli vybraté na základe meraní ich elektrických parametrov (dôležité hlavne pre vysokofrekvenčnú časť). Bohužiaľ oblasť, v ktorej sa ale nesmú robiť kompromisy sú kvalitné plošné spoje. Moduly zosilňovača, atenuátora a riadenia sú postavené na dvojvrstvových doskách s prekovenými otvormi. Z dôvodu vysokých pracovných frekvencií DDS čipu je na zachovanie signálovej integrity nutné použiť aspoň trojvrstvovú dosku. Návrh je ale optimalizovaný tak, aby mala len minimálne nutné rozmery, takže ostáva cenovo prístupná aj pre domáceho kutila.

Technické parametre modulov (t.j. aj generátora) boli zvolené triezvo, tak aby boli dosiahnuteľné a dobre reprodukovateľné aj v domácich podmienkach. Všetky deklarované parametre boli skutočne dosiahnuté a sú podložené meraniami.

Výrobné podklady na dosky plošných spojov sú voľne stiahnuteľné na adrese www.cern.ch/dvaluch/DDS, a po dohode s firmou Printed sú taktiež všetky plošné spoje dostupné formou dobierky.

Princíp generácie signálov metódou priamej číslicovej syntézy

Princíp generácie signálov pomocou priamej číslicovej syntézy je známy už niekoľko desaťročí. Až prudký rozvoj digitálnej techniky a zvýšenie rýchlosti číslicovo analógových prevodníkov o niekoľko rádov umožnili vytvoriť priame číslicové syntezátory špičkových parametrov v integrovanej forme, ktoré sú cenovo prístupné aj pre amatérske využitie.

Priamy číslicový syntezátor predstavuje číslicovo riadený oscilátor. Vstupom takéhoto oscilátora sú hodnoty v riadiacom registri a výstupom je frekvencia, ktorá zodpovedá tejto hodnote. Tvar výstupného signálu je definovaný vyhľadávacími tabuľkami v čipe syntezátora. Väčšina DDS čipov generuje sínusový priebeh.

Akumulátor fázy

Zjednodušený princíp činnosti priameho číslicového syntezátora je znázornený na obrázku 1. Obvod DDS pozostáva z akumulátora fázy, prevodníka fáza/amplitúda a výstupného DA prevodníka. Vzhľadom na to, že sínus je nelineárna funkcia, je zložité signály tohoto tvaru generovať priamo. Preto DDS generátory pracujú ako s primárnou veličinou s fázou. Táto vždy narastá lineárne s časom a ľahko sa teda spracováva číslicovými obvodmi. Akumulátor fázy obsahuje informáciu o okamžitej fáze výstupného signálu, ktorá sa každým „tikom“ hodinového signálu inkrementuje o konštantu reprezentovanú riadiacim slovom.

Obrázok 1: Princíp činnosti priameho číslicového syntezátora

Celá perióda sínusového signálu 2p je rozdelená na 2M krokov, kde M je počet bitov riadiaceho slova. Riadiace slovo určuje veľkosť inkrementu ako celočíselný násobok elementárneho kroku fázy. Čím je riadiace slovo väčšie, tým rýchlejšie rastie fáza a generovaná frekvencia je vyššia.

Výstupnú frekvenciu priameho číslicového syntezátora môžeme teda vyjadriť ako:

![]() (1)

(1)

kde N je riadiace slovo, M počet bitov riadiaceho slova a fREF referenčná frekvencia.

Z princípu fungovania akumulátora fázy vyplýva veľmi dôležitá vlastnosť priamych číslicových syntezátorov – fázovo spojité ladenie. Pri akejkoľvek zmene ladiaceho slova začne fáza len rýchlejšie/pomalšie narastať, čo spôsobí okamžitý a spojitý prechod na novú frekvenciu (obr. 2).

Obrázok 2: Fázovo spojitý prechod na novú frekvenciu. Horná krivka znázoňuje signál prepínajúci frekvencie, dolná je výstup DDS.

Z princípu fungovania akumulátora fázy taktiež vyplýva aj pre niektoré aplikácie negatívna vlastnosť – výstupná frekvencia môže byť jedine racionálnym násobkom vstupnej frekvencie (faktor N/2M vo vzťahu 1). V praxi to môže napríklad znamenať, že výstupná frekvencia môže byť buď 9 999 999,999 998 Hz alebo 10 000 000,000 002 Hz. Nikdy ale nie presne 10 000 000,000 000Hz. Môžeme konštatovať, že pre väčšinu aplikácií to nepredstavuje problém, ale v niektorých kritických aplikáciách kde je potrebný úplne presný násobok vstupnej frekvencie je potom potrebné použiť klasické fázové závesy.

Prevod fáza – amplitúda, čistota spektra výstupného signálu

Výstup z akumulátora fázy je privedený do prevodníka fáza-amplitúda, ktorého úlohou je previesť informáciu o okamžitej fáze na prúd, alebo napätie zodpovedajúce generovanému priebehu. V priemysle sa takmer výlučne používajú generátory sínusového priebehu, ale vo všeobecnosti môže byť generovaný ľubovoľný priebeh. Prevodník fáza-amplitúda je najčastejšie realizovaný pamäťou ROM s uloženým priebehom generovanej funkcie.

Posledným článkom reťazca je číslicovo-analógový prevodník, ktorý prevádza vypočítanú hodnotu generovanej funkcie na analógové napätie alebo prúd. Práve na D/A prevodník sa kladú vysoké kvalitatívne požiadavky a je kritickou časťou celého syntezátora. Vzhľadom na to, že ide o klasický číslicovo-analógový prevod musí byť splnené Nyquistovo kritérium (vo východnom bloku známe ako Shanon-Koteľnikova teoréma) t.j. signál musí byť vzorkovaný minimálne dvojnásobnou frekvenciou akú má jeho najvyššia harmonická zložka. Pokiaľ teda chceme generovať vysokofrekvenčné signály, veľmi ľahko sa dostaneme do oblasti prevodníkov s požadovanou rýchlosťou stoviek Msps až jednotiek Gsps.

Čistota spektra generovaného signálu je primárne určená bitovým rozlíšením DA prevodníka DDS čipu. Počet bitov výstupného D/A prevodníka je parameter, ktorý určuje presnosť s akou sa podarí zrekonštruovať výstupný (sínusový) signál a teda čistotu výstupného spektra DDS generátora. Z teórie spracovania signálov je chyba spôsobená digitalizáciou analógového signálu prevodníkom s konečným počtom bitov známa ako kvantizačný šum. Výkon kvantizačného šumu je vypočítateľný a pomer výkonu užitočného signálu ku kvantizačnému šumu SQR (v dB) vyjadruje vzťah:

![]() (2)

(2)

kde B je rozlíšenie prevodníka v bitoch.

Tento vzťah bol však odvodený pre signály s plnou amplitúdou. Pokiaľ prevodník pracuje so signálom s menšou amplitúdou hodnota SQR sa ďalej zhoršuje, lebo výkon kvantizačného šumu ostáva konštantný, ale výkon signálu je nižší.

Vzťah (3) zohľadňuje aj amplitúdu užitočného signálu:

![]() (3)

(3)

Kde A je pomer amplitúd generovaného signálu ku plnému rozsahu.

Bežne používané DDS čipy sú osadené prevodníkmi s rozlíšením 10 až 14 bitov. V tabuľke 1 je hodnota SQR vypočítaná pre niekoľko typických bitových rozlíšení a pracovných parametrov DDS čipov.

Tabuľka 1: Teoretické hodnoty pomeru užitočného signálu k šumu pre rôzne typy DDS čipov a pracovných módov.

Kvantizačný šum však nie je jediným zdrojom nežiadúcich signálov na výstupe priameho číslicového syntezátora. Ak by mal mať prevodník fázy na amplitúdu (obr. 1) rovnaký počet stavov ako akumulátor fázy veľmi ľahko by sme sa dostali ku vyhľadávacej tabuľke o veľkosti niekoľkých gigabajtov. Takáto tabuľka ale nie je potrebná a len časť najvyšších bitov akumulátora fázy sa privádza do vyhľadávacej tabuľky a zvyšok sa jednoducho ignoruje. Hodnota okamžitej fázy sa takto „zaokrúhľuje“ čím sa do výstupného signálu pridávajú periodicky sa opakujúce chybové signály, ktoré vo frekvenčnej oblasti predstavujú ďalšie nežiadúce spektrálne čiary (obrázok 4, signály označené číslom 12).

Presný mechanizmus vzniku týchto signálov je pomerne obsiahly a je ho možné nájsť napríklad v [2]. Záver pre užívateľa je ten, že čistota spektra výstupného signálu sa dá ovplyvňovať starostlivou voľbou ladiaceho slova. Pre niektoré hodnoty má spektrum značné množstvo nežiadúcich signálov a pre niektoré hodnoty tieto signály nevznikajú vôbec.

Celkovú čistotu výstupného spektra vyjadruje parameter SFDR (Spurious Free Dynamic Range). Zahŕňa všetky nežiadúce signály v spektre a vyjadruje rozdiel medzi najvyššou amplitúdou užitočného signálu a amplitúdou najvyššej nežiadúcej zložky v spektre výstupného signálu syntezátora.

Rekonštrukcia výstupného analógového signálu

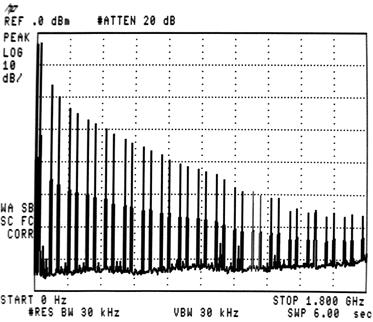

Ako už bolo spomenuté v sekcii o čistote spektra DDS, výstupom syntezátora je D/A prevodník. Na jeho výstupe preto nájdeme okrem generovaného signálu celé spektrum signálov, ktoré podľa vzorkovacej teórie vznikajú zrkadlením generovaného signálu okolo celočíselných násobkov vzorkovacej frekvencie teoreticky až do nekonečna. Zmerané spektrum výstupného signálu syntezátora AD9858 je na obrázku 3. Obvod pracoval na hodinovej frekvencii (fREF) 100MHz a generoval signál s frekvenciou 20MHz. Spektrum je zobrazené od nuly do 1,8GHz.

Obr. 3: Zmerané spektrum výstupného signálu syntezátora AD9858.

Na výstupe D/A prevodníka preto musí byť použitý rekonštrukčný filter, ktorý zabezpečí výber len požadovaného generovaného signálu. Pri „klasickej“ aplikácii obvodu DDS predpokladáme generovanie signálov s frekvenciou od 0 do fREF/2. V tomto prípade je teda nutné použiť rekonštrukčný filter typu dolná priepusť, ktorý v ideálnom prípade potlačí všetky signály s frekvenciami vyššími ako fREF/2. Výber reálneho filtra potom závisí od konkrétnej aplikácie. S reálnymi filtrami je tak možné získať použiteľné signály do približne 30% vzorkovacej frekvencie.

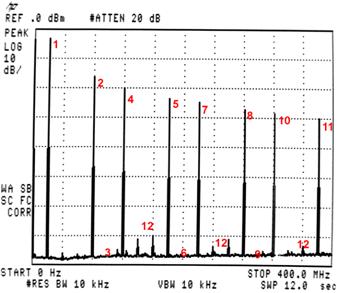

Vzhľadom na to, že spektrum výstupného signálu obsahuje množstvo produktov D/A prevodu, je možné vhodnou voľbou výstupného filtra vybrať aj inú časť spektra a generovať signály v oveľa širšom pásme ako 0 až fREF/2. Na obrázku 4 je zväčšená časť spektra meraného synezátora od nuly do 400MHz.

Obr. 4: Detail spektra do 400MHz.

Jednotlivé spektrálne čiary predstavujú signály s frekvenciami:

1 – základný mód fOUT = 20 MHz

2 – zrkadlová frekvencia fREF-fOUT = 80 MHz

3 – potlačená hodinová frekvencia fREF = 100 MHz

4 – zrkadlová frekvencia fREF+fOUT = 120 MHz

5 – zrkadlová frekvencia 2*fREF-fOUT = 180 MHz

6 – potlačená hodinová frekvencia 2*fREF = 200 MHz

7 – zrkadlová frekvencia 2*fREF+fOUT = 220 MHz

8 – zrkadlová frekvencia 3*fREF-fOUT = 280 MHz

9 – potlačená hodinová frekvencia 3*fREF = 300 MHz

10 – zrkadlová frekvencia 3*fREF+fOUT = 320 MHz

11 – zrkadlová frekvencia 4*fREF-fOUT = 380 MHz

12 – nežiadúce produkty syntézy

Na internete je možné nájsť celú radu aplikačných poznámok o tomto pracovnom móde syntezátora. Na konferencii ŠVOČ v Bratislave v roku 2000 sme s kolegom Labancom publikovali prácu Využitie vyšších módov v priamej číslicovej syntéze frekvencie [1].

Prehľad dostupných obvodov DDS

Zrejme najvýznamnejším hráčom na trhu priamych číslicových syntezátorov je firma Analog Devices (AD). Tabuľka 2 poskytuje stručný prehľad dostupných obvodov od AD rozdelených do súvisejúcich skupín aj s ich základnými parametrami.

Tabuľka 2: Prehľad DDS obvodov od firmy Analog Devices

Referencie

[1] Labanc A., Valúch D.: Využitie vyšších módov v priamej číslicovej syntéze frekvencie. Bratislava, 2000. Článok je prístupný na adrese http://www.balu.sk/skola/svoc2000.pdf

[2] Firemná literatúra Analog Devices: A Technical Tutorial on Digital Signal Synthesis. http://www.analog.com/UploadedFiles/Tutorials/450968421DDS_Tutorial_rev12-2-99.pdf